# Mass Production Testing of the Anode Front-End Electronics for the CMS Endcap Muon Cathode Chambers

A. Golyash \*, N. Bondar \*, T. Ferguson \*\*, L. Sergeev \*, N. Terentiev \*\*, I. Vorobiev \*\*

\*) Petersburg Nuclear Physics Institute, Gatchina, 188350, Russia

\*\*) Carnegie Mellon University, Pittsburgh, PA 15213, USA

(e-mail: golyash@fnal.gov)

- Introduction

- General Structure of the Test Stand and Measurement Techniques

- The Anode Front-End Electronics Test Steps for CMP16 Chips and AD16 Boards

- Data Analysis and Test Results for AD16 Boards

- Delay Chip Certification Test

- Conclusions

# Introduction

# Front-End Electronics for CMS Endcap Muon Chambers

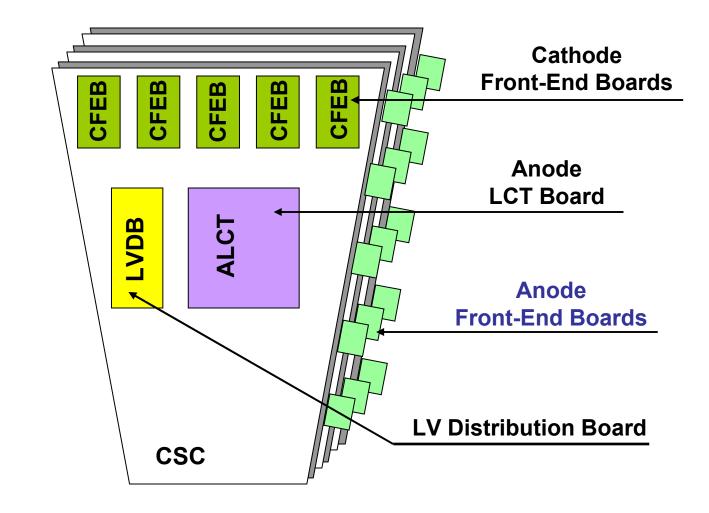

# **Anode Front-End Electronics**

- Provide with high efficiency precise muon timing information for the LHC bunch crossing number identification at the Level-1 trigger.

- Find the location of charged particle tracks with a time accuracy of one bunch crossing of 25 ns.

# Introduction

# **Anode Front-End Electronics Structure**

- Large number of channels (10,000 boards/ 160,000 channels).

- Long term operation time (at least 10 years) with limited maintenance access.

# **The Mass Production Test Goals**

- Assure the quality of the anode front-end electronics:

- 1. reliability,

- 2. channel and board uniformity,

- 3. adequate timing performance.

- Measure and certify the basic parameters of the boards.

- Produce complete documentation for installation checkout, commissioning and maintenance.

The mass production test data and results are stored in a production database for detector calibration and simulation purposes, as well as for board traceability.

### General Structure of the Test Stand and Measurement Techniques

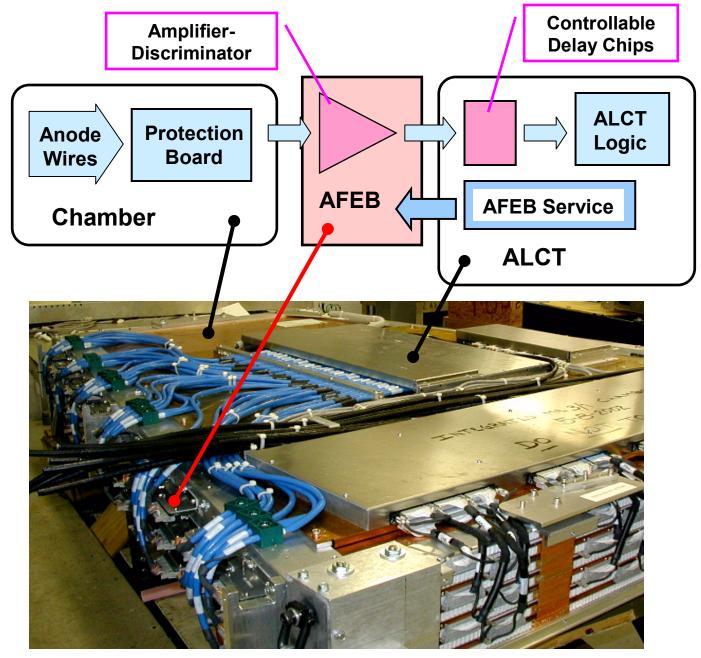

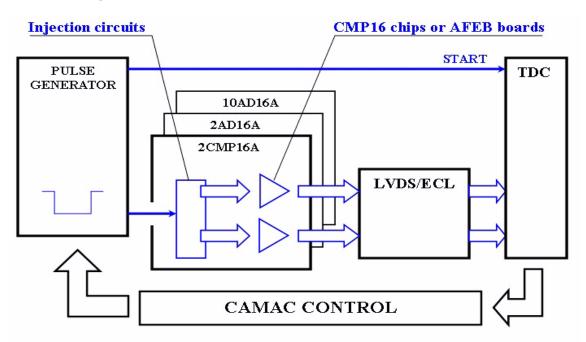

#### Structure of the CMP16 ASIC and AD16 board test stands

# A special set of test equipment, techniques and corresponding software were developed and used.

# A standard module set for the test stands consists of

- specially designed precise Pulse Generator and

- LeCroy 3377 TDC.

#### Pulse Generator (CAMAC)

- 2 channel pulse generator (programmable amplitude, 10 ns rise time).

- 32 channel LVDS/ECL converter

- Provides power and threshold voltage for AD16 boards

### General Structure of the Test Stand and Measurement Techniques

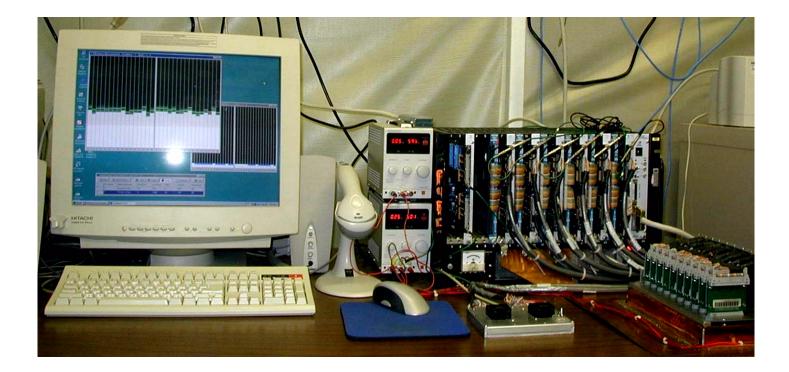

# General View of the CMP16 ASIC and AD16 board test stand

### General Structure of the Test Stand and Measurement Techniques

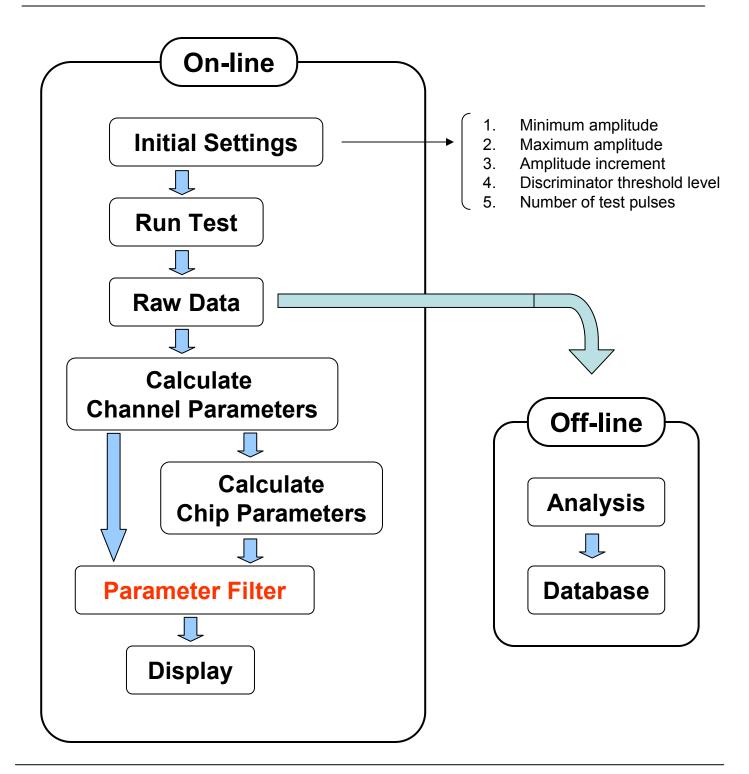

### **Test Stand Measurement Procedure**

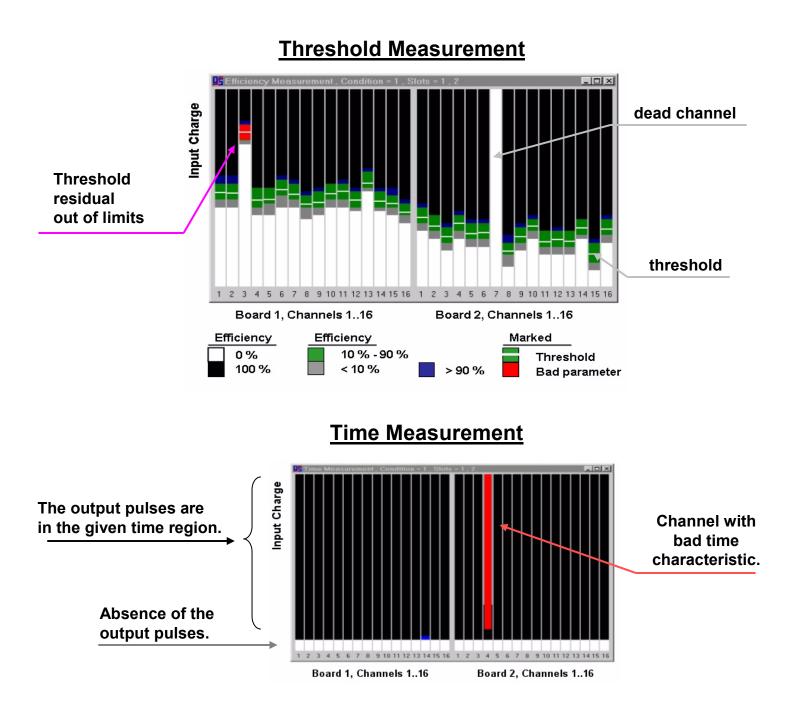

# Test Stand Displays for AD16 boards and CMP16 chips

### The Anode Front-End Electronics Test Steps for CMP16 Chips and AD16 Boards

# **Step1: Selection Procedure for CMP16 Chips**

#### <u>Goal</u>

• Acceptance for installation on the AD16 boards

#### Acceptance criteria

- Current consumption (100 mA ± 10%)

- Functionality of all channels

- The critical dynamic parameters are within the allowed range

#### **Measurements**

- Threshold measurement

- Time measurement

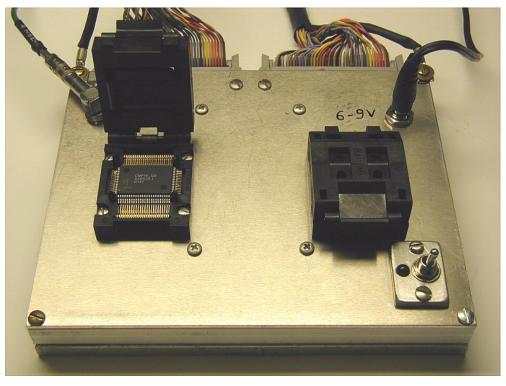

#### 2CMP16A Adapter for two CMP16 ASICs

# **Step 2: Functionality Test for AD16 Boards**

Performed by AD16 manufacturer after board assembly.

### <u>Goals</u>

- Check the board functionality

- Assure the quality of the board assembly

#### **Measurement**

Threshold measurement

#### 2AD16A Adapter for two AD16 boards

### The Anode Front-End Electronics Test Steps for CMP16 Chips and AD16 Boards

#### **Burn-in Procedure for AD16 Boards** Step 3:

#### <u>Goals</u>

- **Detect hidden defects** •

- Increase the board reliability

#### **Conditions**

- 90°C **Temperature** Duration 72 hours

- Powered and pulsed

#### The burn-in time is ~ 1% of the equivalent AD16 board reliability test duration.

The estimation of the AFEB reliability was made earlier by burning in 100 boards in an oven for 4000 hours at a temperature of 110°C (equivalent to about 7 years of real operation at 30°C).

Setup for burn-in of AD16 boards (200 boards tested simultaneously)

- **Total tested**

- 12,200 boards Found not operational 30 boards (all failures were due to bad solder joints, with no chip failures)

**Step 4:** Final Test and Certification of AD16 Boards

#### <u>Goals</u>

- Functionality checking after burn in test.

- Measurement and certification of the critical board parameters.

Each board is measured four times at different conditions (adapter emulates the detector capacitance of 180 pF).

1-2. Threshold measurements at discriminator threshold level (Vth) of 150 and 300 mV (through external test capacitance)

#### Calculated parameters:

- Threshold, Noise,

- Gain, (transfer function),

- Threshold Offset.

- 3. Threshold measurement at Vth = 150 mV (through internal test capacitances)

**Calculated parameter:**

- Internal test capacitance

- 4. Time measurement at Vth = 150 mV

#### **Calculated parameters:**

- Propagation time

- Time resolution

- Slewing time

## The Anode Front-End Electronics Test Steps for CMP16 Chips and AD16 Boards

Step 4: (continue)

10AD16A Adapter for final test and certification of ten AD16 boards.

# **Off-line Analysis (ROOT). Threshold and Noise**

# **Calculated parameters for each channel:**

threshold and noise from the threshold curve 400 Number of the output pulses fitted by a cumulative 350 distribution function 300 which includes 250 a Gaussian error Threshold 200 function 150 gain, 100 discriminator offset 50 internal test 0 capacitance

24

26

28

30

32

34

36

Input charge, fC

38

### Calculated board parameters and certification cuts:

- all listed above parameters averaged over 16 channels

- maximum deviation from average for all parameters

- maximum noise

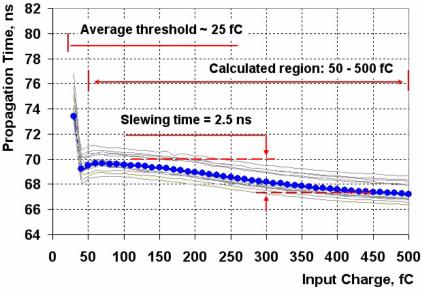

# **Off-line Analysis (ROOT). Timing Parameters**

# Parameters for each channel:

- propagation and slewing time from propagation time vs.

input charge curve <u>9</u> 82 -

- time resolution from resolution time vs. input charge curve

- all of the above for input charge of 50, 100 and 150 fC

- slewing time for input charge of 50 – 500 fC

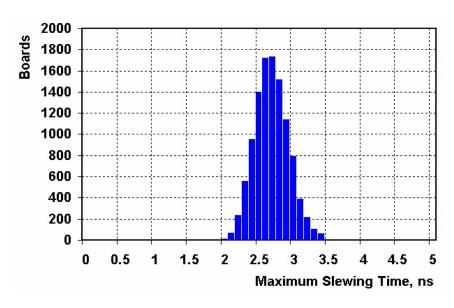

# **Board parameters and certification cuts:**

- all listed above parameters averaged over 16 channels

- maximum deviation from average for all parameters

- maximum resolution and maximum slewing time

# **Production Database**

# Implementation:

- Oracle application on the central CERN Oracle database

- accessible through the Web (using the Oracle9i Application Server)

# Content:

- raw data, test conditions, calibration constants

- results of off-line analysis per channel/board (Text and Postscript files, all measured parameters)

# <u>Goals:</u>

- documentation, board traceability

- use by Final Assembly and Testing sites in the USA, China and Russia

- use in detector simulation and calibration

- use during CMS operation

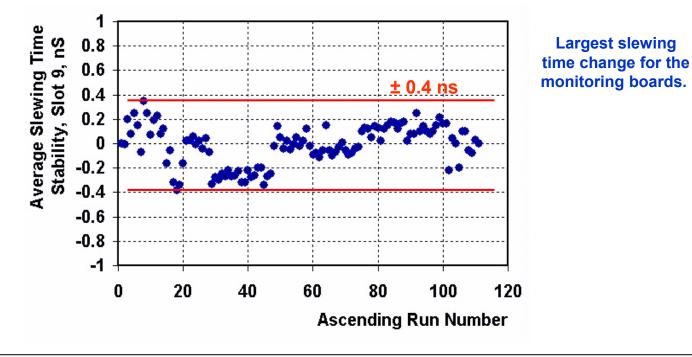

# **10AD16A Test Stand Stability Monitoring**

#### The stability of the AFEB test stand is monitored through data taken each day using the same set of ten boards assigned to each of the 10 slots of the 10AD16A adapter.

| Parameter                              | Maximum Deviation |

|----------------------------------------|-------------------|

| Threshold (fC)                         | ± 1.3             |

| Noise (fC) at Cdet = 180 pF            | ± 0.1             |

| Transfer function (gain, mV/fC)        | ± 0.3             |

| Discriminator offset (mV)              | ± 5.0             |

| CMP16 chip internal capacitance (pF)   | ± 0.01            |

| Propagation time (ns)                  | ± 1.2             |

| Slewing time (ns) at Qin = 50 – 550 fC | ± 0.4             |

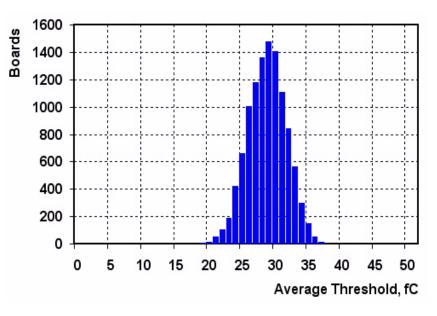

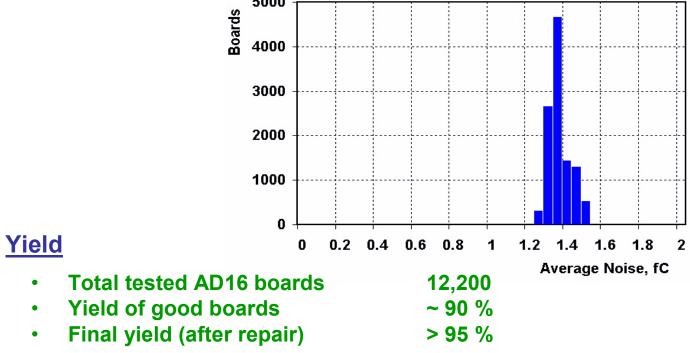

# **Test Result Summary for AD16 Boards**

## Measured parameters for certified AD16 boards.

| Parameter                              | Average ± RMS | Uniformity * |

|----------------------------------------|---------------|--------------|

| Threshold (fC)                         | 29.2 ± 2.9    | 0.9          |

| Noise (fC) at Cdet = 180 pF            | 1.4 ± 0.06    | 0.05         |

| Transfer function (gain, mV/fC)        | 6.9 ± 0.3     | 0.07         |

| Discriminator offset (mV)              | 50 ± 19       | 6            |

| CMP16 chip internal Capacitance (pF)   | 0.24 ± 0.02   | 0.01         |

| Propagation time (ns)                  | 66.5 ± 1.5    | 0.3          |

| Slewing time (ns) at Qin = 50 – 550 fC | 2.4 ± 0.2     | 0.2          |

\*) Uniformity - the standard deviation (RMS) of the channel residual within each board.

# **Delay Chip Certification Test**

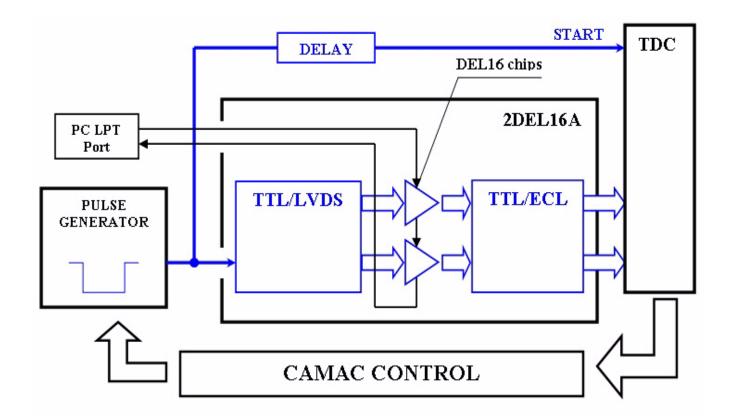

# **DEL16 test stand structure**

## **Test Stand Equipment**

- Pulse generator

- TDC as main DAQ module

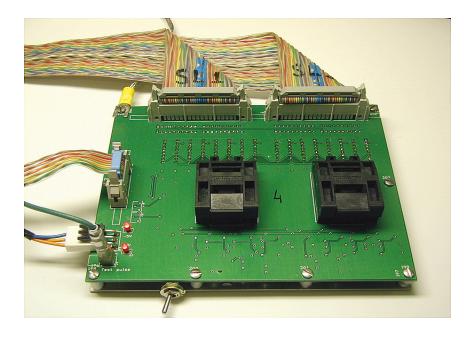

- 2DEL16A adapter

The propagation time of the delay chips is controlled through a PC LPT port which varies the delay code from 0 to 15.

# **Delay Chip Certification Test**

# **DEL16 Delay Chips Certification**

### <u>Goal</u>

Acceptance for installation on the ALCT boards

#### Acceptance criteria

- Functionality of all channels

- Delay uniformity at each delay code

- Linearity of the delay time versus delay code

The selection of the good delay chips is made online using the test stand.

#### **Measurements**

- Test level feature checking of the chip

- Propagation time versus delay code

2DEL16A adapter for two DEL16 chips

# **Test Result Summary for DEL16 Chips**

### Parameters for certified DEL16 chips

| Parameter                       | Average<br>Value | Maximum<br>deviation<br>within chip |

|---------------------------------|------------------|-------------------------------------|

| Propagation time, code = 0, ns  | 19.5 – 24.0      | ± 1.0                               |

| Propagation time, code = 15, ns | 42.0 - 60.0      | ± 1.5                               |

| Slope, ns/LSB                   | 1.0 - 3.0        | ± 0.15                              |

| Maximum nonlinearity, ns        |                  | ± 2.0                               |

## Main Problem

Contact degradation of the commercial clamshell (replaced regularly after 3000 connections)

### **Yield**

- Total tested delay chips 24,000

- Yield of accepted chips 88 %

- For ALCT board production 78 % (of the accepted chips)

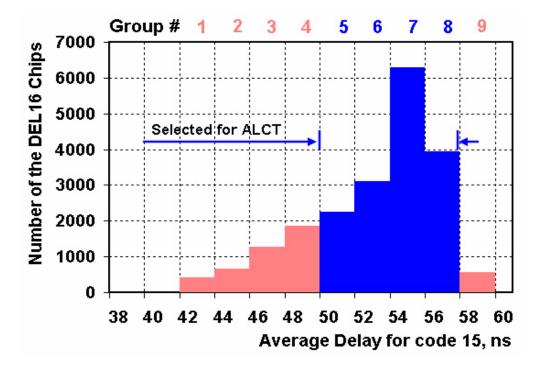

## Grouping of the accepted delay chips for assembly on the ALCT boards

Due to the technological spread of the average delay step, the accepted chips were divided into 9 separate groups, each having a 2 ns wide bin in the distribution of the average chip delay at delay code of 15.

Group from 5 to 8 used for ALCT board production.

The average delay steps can be tuned later on the ALCT boards.

- We developed and successfully used a specialized set of test equipment, technique and corresponding software.

- The quantity of certified electronics are enough to equip all the chambers of the CMS Muon Endcap System.

- We tested all anode front end boards AD16 and delay chips DEL16.